Aerospace Data Storage and Processing Systems

#### Achieving High Performance Computing and Application Flexibility within the Spacecraft Payload

Ian Troxel, Matthew Fehringer, Michael Chenoweth, and Paul Murray

SEAKR Engineering, Inc.

Centennial, CO

Military and Aerospace Programmable Logic Devices (MAPLD) Conference Annapolis, MD September 16-18, 2008

#### Motivation

- o Faster, better, cheaper often no longer just picking two!

- o Mission requirements increasing

- Higher resolution data acquisition driving processing and storage requirements

- Onboard processing and/or downlink often the system bottleneck

- Increased need for autonomous functionality affecting system "overhead"

- o Design challenges keeping pace

- SWaP limitations on payloads not relaxing

- Flexible, multiuse payloads sought to limit NRE

- Use of Commercial-Off-The-Shelf (COTS) devices

- "Radiation-hardened" components often not cost-effective for highperformance applications

- COTS provide improved performance but typically require mitigation to achieve the same level of fault tolerance

- Reconfigurable Computing (RCCs) devices

- Typically improve performance/Watt for amenable application classes

- Reconfigurability offers increased payload flexibility

## **HPC** with Flexibility

Aerospace Data Storage and Processing Systems

- o Application Independent Processor (AIP) Features

- Mixture of scalar processors and RCCs

- Reconfigurable on-orbit

- Flexible, scalable architecture

- Usage of open standards

- SEE Tolerant system

- Flexible I/O architecture

- **o** Designed for Responsive Space

- Low cost, high performance

- Rapid deployment through adaptability

- Designed for multiple missions

- o Missions To Date

- Advanced Responsive Tactically Effective Military Imaging Spectrometer (ARTEMIS)

- Programmable Space Transceiver (PST)

- Programmable Space IP Modem (PSIM)

- Orion Vision Processing Unit (VPU)

- JPEG2K image compression

**ARTEMIS Configuration of AIP**

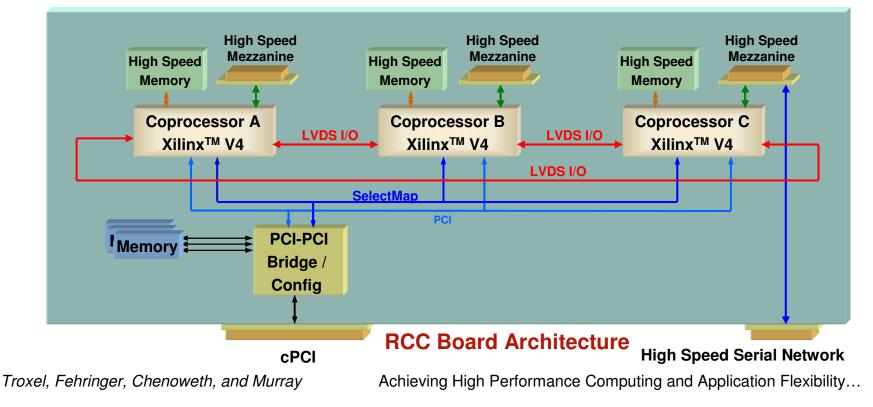

### **AIP System Architecture**

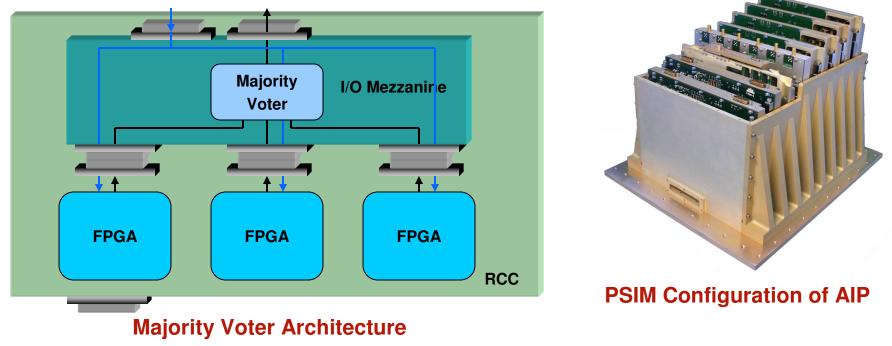

- o Reconfigurable Computer Board(s)

- Xilinx<sup>™</sup> V4, high-speed memory and SERDES backplane

- o COTS PowerPC<sup>™</sup>-based SBC(s)

- 600 DMIPs, 1.2 GFLOP, Gigabit Ethernet and Spacewire

- o Memory and I/O personality mezzanine cards

- 16 GBytes flash memory, camera link, analog, digital developed to date

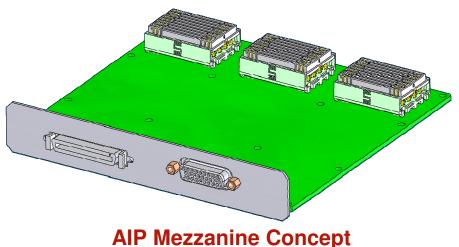

#### **AIP Personality Mezz. Card**

#### Aerospace Data Storage and Processing Systems

- Personality Mezzanine for applicationspecific functionality

- Lower risk, quick development, lower costs

- I/O and unique I/O connectors

- Memory

- Logic

- TMR mitigation

- Analog circuitry ADC/DAC

- o High speed mezzanine connectors

- 170 high speed I/O

- LVDS

- High speed serial

- TMR'd signals

- Symmetrical Design to all Xilinx<sup>™</sup> FPGAs

- o Fault tolerance options

- "Radiation hardened" voter on the mezz.

- Partial TMR

- SEAKR replay capability provides temporal redundancy

- Combinations

#### **ARTEMIS Mezzanine**

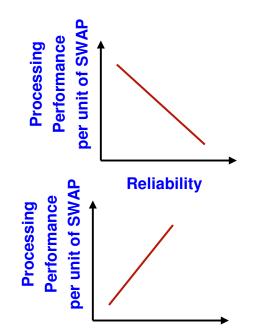

## **AIP SEE Mitigation**

- One size does not fit all

- o Mitigation methods are highly application dependant

- SWAP constraints

- Processing performance

- Reliability requirements

- Design schedule

- Type of data and peripherals

- Latency constraints

- Factors need to be weighed before an approach can be implemented

- o Optimum designs may use a quiver of mitigation methods

- Combination of HW and SW

- AIP personality mezzanine card provides fault tolerance options

Troxel, Fehringer, Chenoweth, and Murray

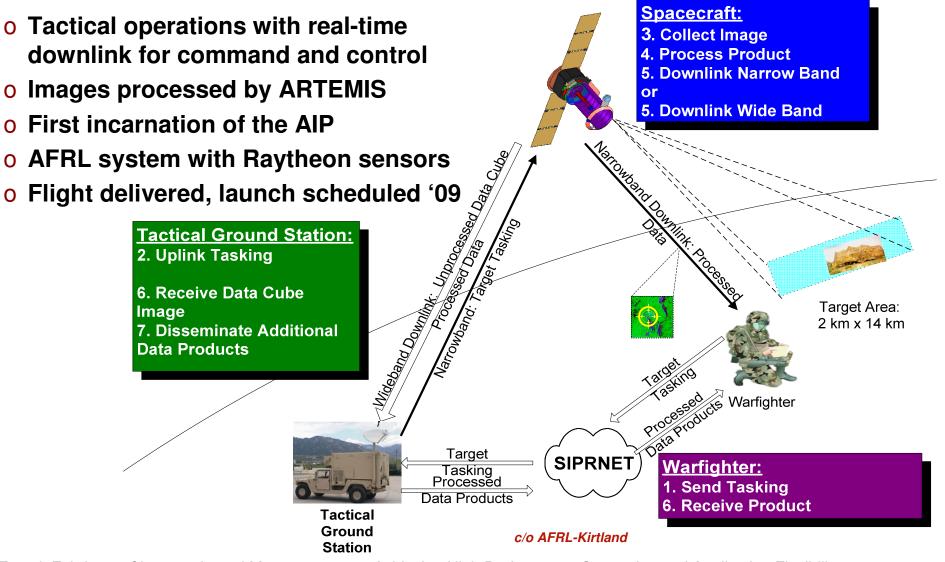

#### **TacSat-3 Mission Summary**

erospace Data Storage and Processing Systems

Troxel, Fehringer, Chenoweth, and Murray

Achieving High Performance Computing and Application Flexibility... 7/17

#### **ARTEMIS Design Highlights**

- o Combination of sequential processor and RCC

- Two Xilinx<sup>™</sup> FPGAs required to meet data throughput from sensors

- FPGAs perform data acquisition and preprocessing functions such as calibration

- Microblaze<sup>™</sup> core coordinates memory accesses and processor communication

- PowerPC<sup>™</sup> SBC dedicated to image generation and target cueing

- Prior generation did not use RCCs because the data processing and SWaP requirements were not as challenging (airborne system)

- RCCs required to meet desired SWaP on spacecraft

- Size: 7.82H x 11.41W x 10.0D inches

- Mass: 18 lbs

- Power: 40 Watts (requirement less than 50W)

- o Configuration scrubbing used for RCC SEU mitigation

- Need to correct control path corruptions

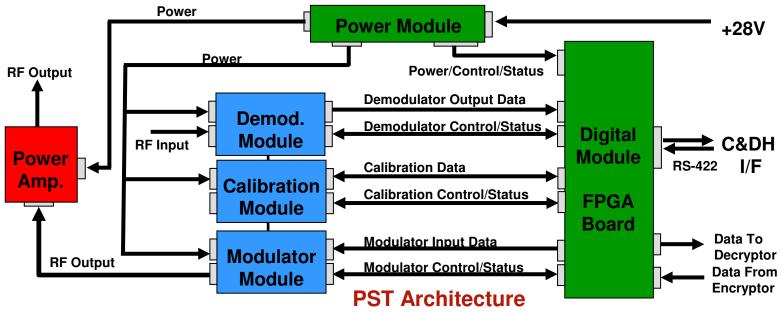

# **PST Mission Summary**

Verospace Data Storage and Processing Systems

Programmable Satellite

Transceiver (PST) provides

frequency agile sat. comm.

- Each band continuously tunable

- Programmable on the ground and/or in flight

- AFRL Enhanced Phase-II SBIR with EM delivered Q2'08

**PST Configuration of AIP**

Troxel, Fehringer, Chenoweth, and Murray

- o Receiver/Uplink

- L-Band 1760 to 1840 MHz

- S-Band 2025 to 2120 MHz

- o Transmitter/Downlink

- S-Band 2200 to 2300 MHz

- o Space Ground Link System (SGLS)

- FSK-AM Command Uplink (1 kbps, 2 kbps)

- Subcarrier BPSK Telemetry Downlink (256 kbps)

- o Universal S-Band (USB)

- Subcarrier BPSK Command Uplink (<= 4 kbps)</li>

- Subcarrier BPSK Telemetry Downlink (256 kbps)

- o Future Waveforms in development

#### **PST Design Highlights**

- **o** FPGA devices form the basis of the Digital Module

- Agile waveform processing performed in Xilinx<sup>™</sup> FPGAs

- Given SWaP requirements, even high-end PowerPCs could not meet specs - 3.86H x 6.85 W x 7.0D inches, Mass: 10 lbs, Power: RX: 16W, TX: 45W

- Waveform processing updated through reconfiguration

- o RCC SEU mitigation

- Xilinx<sup>™</sup> configuration scrubbing used for SEU mitigation to correct control path

- Memory interfaces replicated in triplicate

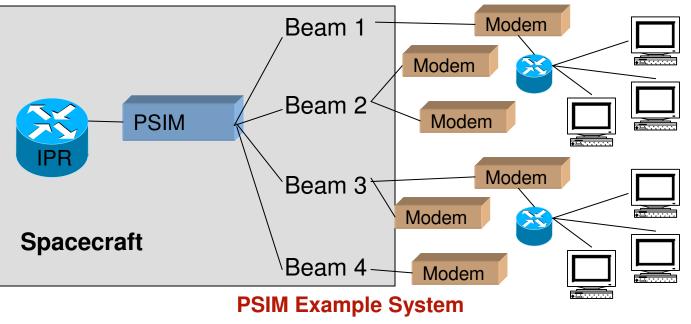

# **PSIM Mission Summary**

- Programmable Satellite

Internet Protocol Modem

(PSIM) translates between

standard sat. comm.

waveforms and IP/Ethernet

- Commercial customer with flight units delivered Q3'08

- Packet-based satellite communication

- Virtual circuit philosophy

- Beam and waveform independent routing

- Advantages over bent-pipe sat. comm.

- Improves scalability and throughput

- Decentralized multicast

- Fine-grained QoS possible

#### **PSIM Design Highlights**

Aerospace Data Storage and Processing Systems

- o Combination of two sequential processors, 12 FPGAs and analog switch card

- FPGAs provide waveform processing

- Processors provide Ethernet interfaces, packet switching

- Leveraging the advantages of each type of component

- o Mezzanine card includes majority voting and router physical interfaces

Troxel, Fehringer, Chenoweth, and Murray

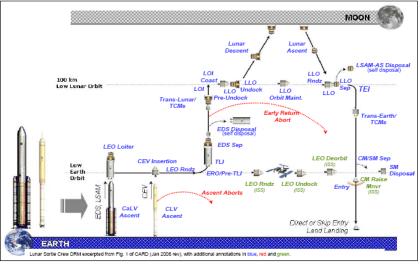

#### **Orion-VPU Mission Summary**

#### Aerospace Data Storage and Processing Systems

- VPU provides a reconfigurable hardware platform for processing image algorithms

- Pose Estimation

- Optical Navigation

- Compression/Decompression

- Receives image data from various Relative Navigation Sensors

- Star Tracker

- Vision Navigation Sensor

- Docking Camera

- Situational Awareness Camera

- Supports rendezvous, proximity operations, docking and un-docking for ISS and Lunar missions

Images c/o Orion Program Office, NASA-Glenn

Achieving High Performance Computing and Application Flexibility... 13/17

#### **ORION-VPU Highlights**

- o Combination of sequential processor and RCC

- Xilinx<sup>™</sup> FPGAs deployed in TMR for high criticality sensor algorithms

- Video processing algorithms (i.e. feature recognition, graphical overlay, tiling, etc.) and video compression video

- Microblaze<sup>™</sup> core coordinates algorithm cores and processor communication

- LEON<sup>™</sup> SBC dedicated to system coordination, error handling, RCC configuration and oversight and interconnect control

- Time-Triggered Gigabit Ethernet PMC and RS422

- o Mezzanine card provides sensor interfaces

- LVDS interfaces with access to all three FPGAs for flexibility in video stream selection and mitigation schemes

- o Configuration scrubbing and TMR for RCC SEU mitigation

- Corrects control path corruptions

#### Conclusions

- o Application Independent Processor developed for space applications

- Supports the responsive space mission (e.g. TacSat-3)

- Reconfigurable on-orbit

- Flexible, scalable architecture

- Mission performance requirements driving the use of commercial devices

- Low cost, high performance

- Designed for multiple missions

- o Flexibility demonstrated on several missions

- Advanced Responsive Tactically Effective Military Imaging Spectrometer (ARTEMIS)

- Programmable Space Transceiver (PST)

- Programmable Space IP Modem (PSIM)

- Orion Vision Processing Unit (VPU)

#### **SEAKR Heritage**

Aerospace Data Storage and Processing Systems

PRODUCT CODE **Memory Systems On-Board Processors Manned Flight Spacecraft Avionics Satellite Communications Other-Than-Space**

Launched 1992 - 1996 1997 - 2000 Clementine ACE APEX MicroLabs RadarSat NEAR Spartan MGS ACTEX

Launched SEASTAR **MARS98** P91 QuickScat **DMSP (F15) MightSat II**

Launched 2001 - 2002 Mars Odvssev GeoLITE Quickbird SAGE III HESSI MMU (Shuttle)

Launched 2003 - 2005 Coriolis ICE Sat GALEX Orbimage (3 & 4) **DMSP (F16)** Gravity Probe B MRO Swift

Launched 2005-2008 **Deep Impact** CloudSat **DMSP (F17)** Cibola P909

JEM HRDR

JEM-SSEDSU

Worldview-1

Kepler Glast

**DMSP 5D3** Challenger HDAS/DAAS LEO LTMPF MAU - C&DH **MMSM** NFMO NPP **RCC-MAP** SRB SSP DSX-ECS DSX-C&DH SBSS-SSR SBSS-C&DH WBDG Worldview-2 **PST** Phoenix Lander SpaceCube WISE-FMC 000 **Digital Channelizer**

Delivered

ARTEMIS

Development VPU NPOESS **SBR-OBP IADMS - NGST** SSP IRIS **RSNIC C-17 MMC iAPS** JWST SSR CEU

SEAKR's product mix shift from nearly 100% SSRs to 25 – 40% SSRs

Troxel, Fehringer, Chenoweth, and Murray

Achieving High Performance Computing and Application Flexibility... 16/17

### **Contact Information**

Aerospace Data Storage and Processing Systems

#### **Dave Jungkind**

Business Development <u>dave.jungkind@SEAKR.com</u>

Dr. Ian Troxel

• 303-784-7673

303-784-7734

Future Systems Architect ian.troxel@SEAKR.com

SEAKR Engineering, Inc. 6221 South Racine Circle Centennial, CO 80111-6427 main: 303 790 8499 fax: 303 790 8720 web: http://www.SEAKR.com